- 您现在的位置:买卖IC网 > Sheet目录1992 > DAC8413EP (Analog Devices Inc)IC DAC 12BIT QUAD V-OUT 28-DIP

DAC8412/DAC8413

Data Sheet

Rev. G | Page 8 of 20

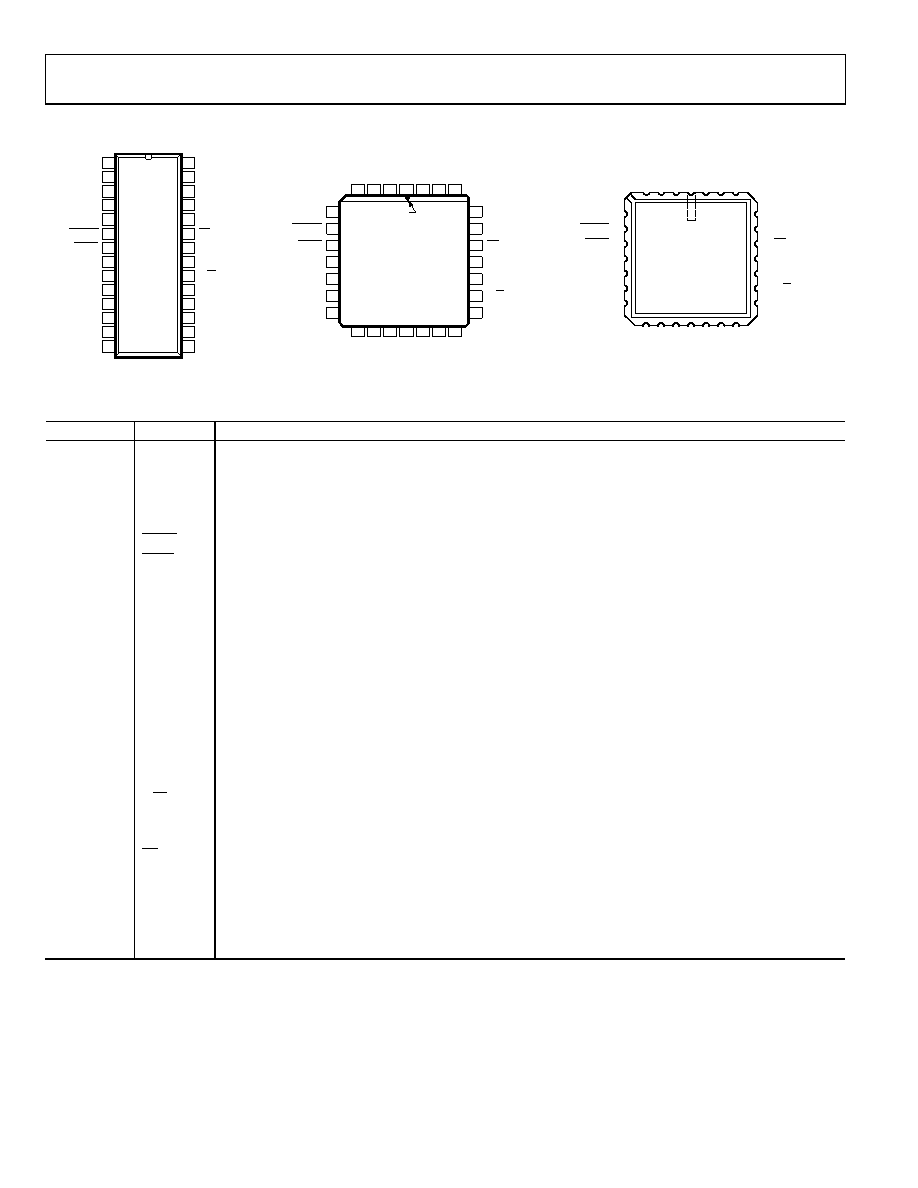

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

VREFH 1

VOUTB 2

VOUTA 3

VSS 4

VREFL

28

VOUTC

27

VOUTD

26

VDD

25

DGND

5

RESET

6

LDAC

7

VLOGIC

24

CS

23

A0

22

DB0 (LSB)

8

A1

21

DB1

9

R/W

20

DB2 10

DB11 (MSB)

19

DB3 11

DB10

18

DB4 12

DB9

17

DB5 13

DB8

16

DB6 14

DB7

15

00

27

4-

00

8

DAC8412/

DAC8413

TOP VIEW

(Not to Scale)

128

27

26

2

3

4

5

6

7

8

9

10

11

25

24

23

22

21

20

19

DGND

RESET

LDAC

DB0 (LSB)

DB1

DB2

DB3

VDD

VLOGIC

CS

A0

A1

R/W

DB11 (MSB)

V

SS

V

OU

T

A

V

OU

T

B

V

RE

F

H

V

RE

F

L

V

OU

T

C

V

OU

T

D

DB

4

DB

5

DB

6

DB

7

DB

8

DB

9

DB10

PIN 1

INDENTFIER

12

13

14

15

16

17

18

00

274

-00

9

DAC8412/

DAC8413

TOP VIEW

(Not to Scale)

00

27

4-

0

10

DAC8412/

DAC8413

TOP VIEW

(Not to Scale)

5

DGND

6

RESET

7

LDAC

8

DB0 (LSB)

9

DB1

10

DB2

11

DB3

25

VDD

24

VLOGIC

23

CS

22

A0

21

A1

20

R/W

19

DB11 (MSB)

26

V

OU

T

D

27

V

OU

T

C

28

V

RE

F

L

1

V

RE

F

H

2

V

OU

T

B

3

V

OU

T

A

4

V

SS

18

DB10

17

DB9

16

DB8

15

DB7

14

DB6

13

DB5

12

DB4

Figure 7. PDIP/CERDIP

Figure 8. PLCC

Figure 9. LCC

Table 5. Pin Function Descriptions

Pin Number

Mnemonic

Description

1

VREFH

High-Side DAC Reference Input.

2

VOUTB

DAC B Output.

3

VOUTA

DAC A Output.

4

VSS

Lower Rail Power Supply.

5

DGND

Digital Ground.

6

RESET

Reset Input and Output Registers to all 0s, Enabled at Active Low.

7

LDAC

Load Data to DAC, Enabled at Active Low.

8

DB0

Data Bit 0, LSB.

9

DB1

Data Bit 1.

10

DB2

Data Bit 2.

11

DB3

Data Bit 3.

12

DB4

Data Bit 4.

13

DB5

Data Bit 5.

14

DB6

Data Bit 6.

15

DB7

Data Bit 7.

16

DB8

Data Bit 8.

17

DB9

Data Bit 9.

18

DB10

Data Bit 10.

19

DB11

Data Bit 11, MSB.

20

R/W

Active Low to Write Data to DAC. Active high to readback previous data at data bit pins with VLOGIC connected to 5 V.

21

A1

Address Bit 1.

22

A0

Address Bit 0.

23

CS

Chip Select, Enabled at Active Low.

24

VLOGIC

Voltage Supply for Readback Function. Can be open circuit if not used.

25

VDD

Upper Rail Power Supply.

26

VOUTD

DAC D Output.

27

VOUTC

DAC C Output.

28

VREFL

Low-Side DAC Reference Input.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

DAC8420FQ

IC DAC 12BIT QUAD SRL LP 16-CDIP

DAC8426EPZ

IC DAC 8BIT QUAD 10VREF 20PDIP

DAC8531IDRBTG4

IC D/A CONV LP 16-BIT 8-SON

DAC8562FP

IC DAC 12BIT PARALLEL 5V 20-DIP

DS1004Z-5+T

IC DELAY LINE 5TAP 25NS 8-SOIC

DS1005-125+

IC DELAY LINE 5TAP 125NS 14-DIP

DS1007S-2+T&R

IC DELAY LINE 4NS 16-SOIC

DS1010S-50+T&R

IC DELAY LINE 10TAP 16-SOIC

相关代理商/技术参数

DAC8413EPZ

功能描述:IC DAC 12BIT QUAD V-OUT 28DIP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS

Obsolescence Mitigation Program 标准包装:1,000 系列:- 设置时间:1µs 位数:8 数据接口:串行 转换器数目:8 电压电源:双 ± 功率耗散(最大):941mW 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:24-SOIC(0.295",7.50mm 宽) 供应商设备封装:24-SOIC W 包装:带卷 (TR) 输出数目和类型:8 电压,单极 采样率(每秒):*

DAC8413FP

功能描述:IC DAC 12BIT QUAD V-OUT 28-DIP RoHS:否 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS

Obsolescence Mitigation Program 标准包装:1,000 系列:- 设置时间:1µs 位数:8 数据接口:串行 转换器数目:8 电压电源:双 ± 功率耗散(最大):941mW 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:24-SOIC(0.295",7.50mm 宽) 供应商设备封装:24-SOIC W 包装:带卷 (TR) 输出数目和类型:8 电压,单极 采样率(每秒):*

DAC8413FPC

功能描述:IC DAC 12BIT QUAD READBK 28-PLCC RoHS:否 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS

Obsolescence Mitigation Program 标准包装:1,000 系列:- 设置时间:1µs 位数:8 数据接口:串行 转换器数目:8 电压电源:双 ± 功率耗散(最大):941mW 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:24-SOIC(0.295",7.50mm 宽) 供应商设备封装:24-SOIC W 包装:带卷 (TR) 输出数目和类型:8 电压,单极 采样率(每秒):*

DAC8413FPC-REEL

功能描述:IC DAC 12BIT QUAD V-OUT 28-PLCC RoHS:否 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 产品培训模块:Data Converter Fundamentals

DAC Architectures 标准包装:750 系列:- 设置时间:7µs 位数:16 数据接口:并联 转换器数目:1 电压电源:双 ± 功率耗散(最大):100mW 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-LCC(J 形引线) 供应商设备封装:28-PLCC(11.51x11.51) 包装:带卷 (TR) 输出数目和类型:1 电压,单极;1 电压,双极 采样率(每秒):143k

DAC8413FPCZ

功能描述:IC DAC 12BIT QUAD READBK 28-PLCC RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS

Obsolescence Mitigation Program 标准包装:1,000 系列:- 设置时间:1µs 位数:8 数据接口:串行 转换器数目:8 电压电源:双 ± 功率耗散(最大):941mW 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:24-SOIC(0.295",7.50mm 宽) 供应商设备封装:24-SOIC W 包装:带卷 (TR) 输出数目和类型:8 电压,单极 采样率(每秒):*

DAC8413FPCZ-REEL

功能描述:IC DAC 12BIT QUAD V-OUT 28PLCC RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 产品培训模块:Data Converter Fundamentals

DAC Architectures 标准包装:750 系列:- 设置时间:7µs 位数:16 数据接口:并联 转换器数目:1 电压电源:双 ± 功率耗散(最大):100mW 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-LCC(J 形引线) 供应商设备封装:28-PLCC(11.51x11.51) 包装:带卷 (TR) 输出数目和类型:1 电压,单极;1 电压,双极 采样率(每秒):143k

DAC8413FPZ

功能描述:IC DAC 12BIT QUAD V-OUT 28DIP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 标准包装:1 系列:- 设置时间:4.5µs 位数:12 数据接口:串行,SPI? 转换器数目:1 电压电源:单电源 功率耗散(最大):- 工作温度:-40°C ~ 125°C 安装类型:表面贴装 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOICN 包装:剪切带 (CT) 输出数目和类型:1 电压,单极;1 电压,双极 采样率(每秒):* 其它名称:MCP4921T-E/SNCTMCP4921T-E/SNRCTMCP4921T-E/SNRCT-ND

dac8413ft

制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Analog Devices 功能描述: